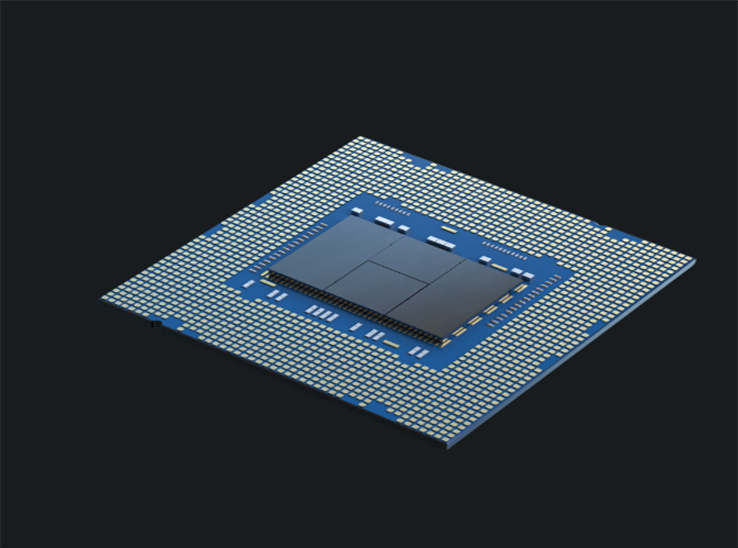

Enhancing

Testability for Reliable Chips.

Design for Testability (DFT) is essential for ensuring high-quality, defect-free semiconductor chips. By implementing robust DFT architectures and methodologies, we enhance fault coverage, improve test efficiency, and reduce overall testing costs. Our expertise spans scan insertion, ATPG pattern generation, memory BIST, and boundary scan techniques.

With a strong focus on first-pass silicon success, our DFT solutions optimize testability while minimizing power and performance impact. From RTL-level checks to post-silicon debug, we provide end-to-end support for seamless chip validation.